据新加坡科技设计大学 (SUTD) 的研究人员称,最近发现的二维 (2D) 半导体系列可以为高性能和节能电子产品铺平道路。他们的发现发表在npj 2D Materials and Applications 上,可能会导致制造适用于主流电子和光电子的半导体器件,甚至有可能完全取代硅基器件技术。

在寻求电子设备小型化的过程中,一个众所周知的趋势是摩尔定律,它描述了计算机集成电路中的组件数量如何每两年翻一番。由于晶体管的尺寸不断减小,这种趋势成为可能,其中一些非常小,以至于数以百万计的晶体管可以塞进一个指甲大小的芯片上。但随着这一趋势的继续,工程师们开始努力应对硅基器件技术固有的材料限制。

“由于量子隧道效应,将硅基晶体管缩小得太小会导致器件行为高度无法控制,”负责这项研究的 SUTD 助理教授 Ang Yee Sin 说。“人们现在正在寻找超越‘硅时代’的新材料,而二维半导体是一个很有前途的候选材料。”

二维半导体是只有几个原子厚的材料。由于它们的纳米级尺寸,在开发紧凑型电子设备的过程中,此类材料是硅替代品的有力竞争者。然而,许多当前可用的 2D 半导体在与金属接触时受到高电阻的困扰。

“当你在金属和半导体之间形成接触时,通常会出现我们所说的肖特基势垒,”Ang 解释说。“为了迫使电力通过这个屏障,你需要施加一个强大的电压,这会浪费电力并产生废热。”

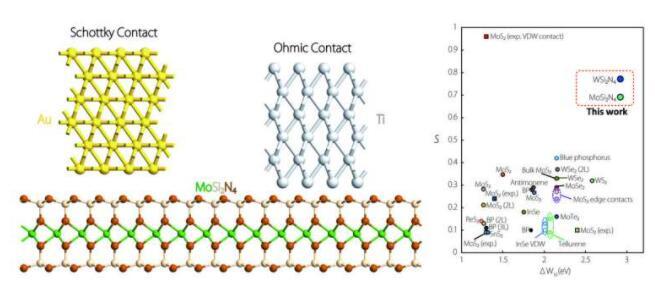

这激起了团队对欧姆接触或没有肖特基势垒的金属-半导体接触的兴趣。在他们的研究中,Ang 和南京大学、新加坡国立大学和浙江大学的合作者表明,最近发现的一个二维半导体家族,即 MoSi 2 N 4和 WSi 2 N 4,与金属钛、钪和镍,广泛用于半导体器件行业。

此外,研究人员还表明,新材料没有费米能级钉扎(FLP),这一问题严重限制了其他二维半导体的应用潜力。

“FLP 是在许多金属-半导体接触中发生的不利影响,是由接触界面处的缺陷和复杂材料相互作用引起的,”Ang 说。“这种效果将触点的电气特性‘固定’在一个很窄的范围内,而不管触点中使用的是什么金属。”

由于 FLP,工程师无法调整或调整金属和半导体之间的肖特基势垒——降低了半导体器件的设计灵活性。

为了最大限度地减少 FLP,工程师通常采用诸如非常轻缓缓慢地将金属放置在 2D 半导体顶部、在金属和半导体之间创建缓冲层或使用 2D 金属作为与 2D 半导体的接触材料等策略。虽然这些方法是可行的,但它们还不实用,并且与使用当今可用的主流工业技术的大规模制造不兼容。

令人惊讶的是,Ang 的团队表明,MoSi 2 N 4和 WSi 2 N 4由于惰性 Si-N 外层可以保护下层半导体层免受接触界面处的缺陷和材料相互作用的影响,因此自然可以免受 FLP 的影响。

由于这种保护,肖特基势垒是“非固定”的,可以进行调整以满足各种应用要求。这种性能改进有助于将 2D 半导体作为硅基技术的替代品投入使用,台积电和三星等主要参与者已经表达了对 2D 半导体电子产品的兴趣。

Ang 希望他们的工作将鼓励其他研究人员探索新发现的 2D半导体家族中更多成员的有趣特性,即使是那些具有电子以外应用的特性。

“其中一些在电子应用方面可能很差,但对于自旋电子学、光催化剂或作为太阳能电池的构建块非常有用,”他总结道。“我们的下一个挑战是系统地扫描所有这些二维材料,并根据它们的潜在应用对其进行分类。”